Overview

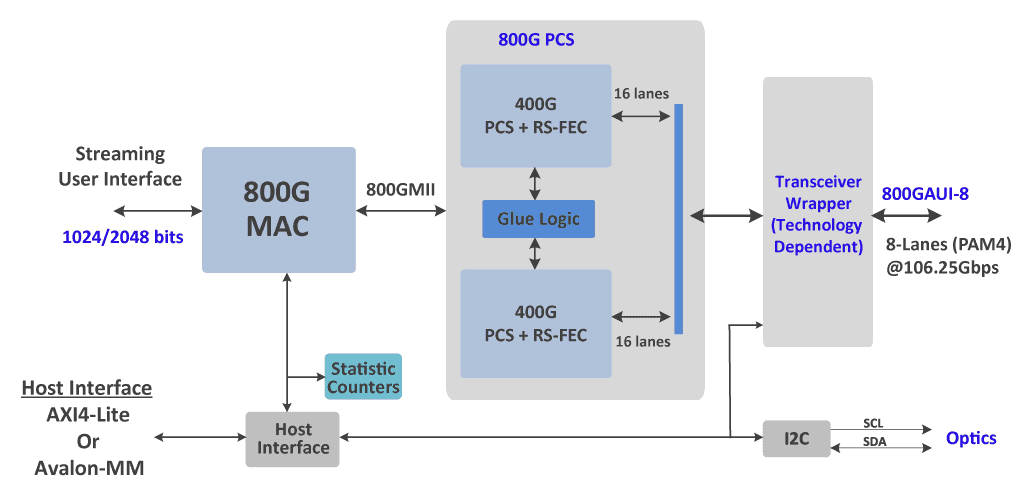

The 800Gbps Ethernet IP solution offers a fully integrated Ethernet Technology Consortium (ETC) compliant solution for use in core networks, Ethernet switching and network interface card (NIC) applications. The Ethernet cores implement an efficient architecture to achieve best in class resource utilization and performance numbers for targeting the complete 800Gbps Ethernet solution to ASICs as well as FPGAs. The ETC 800G Ethernet is designed as an interface that uses eight 106Gb/s lanes using two IEEE802.3 400G PCS instances with a single IEEE802.3 compliant 800G MAC.

Features

- Two 400GBase-R PCS cores with required modifications and glue logic.

- Includes RS-FEC(544,514) KP4 FEC

- 800Gbps MAC core with streaming user interface.

- Technology dependent transceiver wrappers for SERDES transceivers.

- RMON block for statistics counters.

- AXI4-Lite or Avalon-MM based fabric for host interface register access.

- MDIO/I2C cores for optical module control and status.

Deliverables

- Encrypted MAC and PCS RTL for simulation and synthesis

- Encrypted L2 packet generator and checker RTL for simulation and synthesis (included in MAC wrapper)

- Source code RTL (Verilog) for top level Ethernet wrappers to allow for user specific customizations.

- Technology specific transceiver wrappers for the selected device family

- Source code RTL (Verilog) for AXI4-Lite and Avalon-MM arbiters and address decoders

- Constraint files and synthesis scripts for design compilation

- Linux based APIs/tools to access core configuration and statistics registers

- Design guide(s) and user manual(s)