Overview

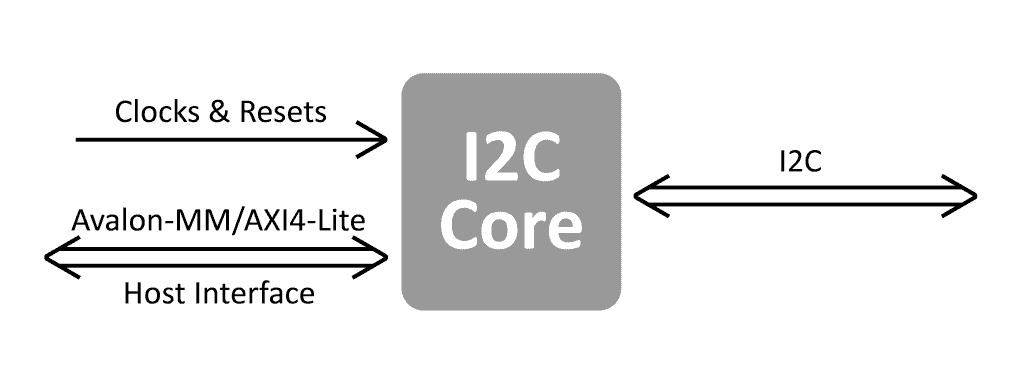

The I2C/SMBus master IP core provides a simple and efficient method of data exchange between devices. I2C is a 2-wire serial bus interface which can be used to access I2C based peripherals such as sensors, EEPROMs and IOT devices.

Features

- Compatible with Philips I2C, SMBus and PMBus standards.

- Programmable host clock division for I2C interface clock generation.

- Programmable I2C transactions possible using a simple custom instruction set and instruction/ data FIFOs.

- Repeated START/STOP condition generation/ detection.

- Programmable I2C slave address per transaction.

- Built in support for transaction timeout and NAK status. Main controller providing byte-level control using FSM and bus interface providing bit-level control.

- Fully compliant to the AXI4-Lite/Avalon-MM interface for register access host interface.

- Interupt and polling support to indicate transaction completion.

- Supporting API/tools available.