Overview

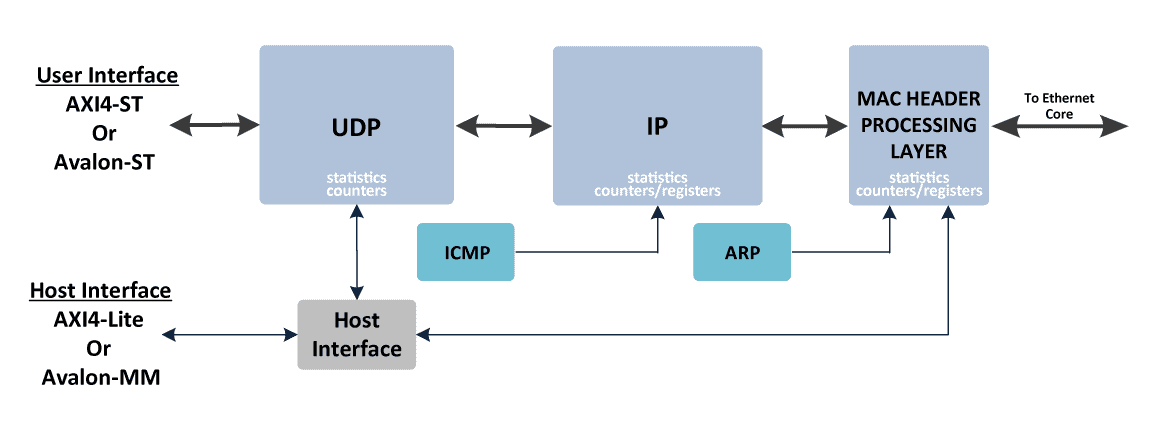

UOE is high performance and highly customizable UDP/IP hardware stack compliant with RFC 768 (for UDP) and RFC 791 (for IPv4)/RFC 2460(for IPv6). The UOE core includes:

- L4 UDP engine

- L3 IPv4/IPv6 engine

- L2 Mac engine

- Statistic counter blocks and user configurable registers

- ARP and ICMP buffers

UOE is designed to be integrated with any Ethernet Solutions that has AXI4-ST/Avalon-ST interface. User interface can be customized for AXI4-ST or Avalon-ST. Data path in addition supports a wide range of interface widths from 32-bit up to 512-bit. Single clock design provides easy manageability for the user.

32-bit user interface runs @ 312.5MHz clock for 10G, 64- bit user interface runs @ 156.25MHz for 10G, 128-bit user interface runs @ 312.5MHz for 40G, 256-bit user interface runs @ 156.25MHz for 40G, and 512-bit user interface runs @ 312.5MHz for 100G.

Core IP layer can be customized for IPv4 or IPv6 depending on the application. The header fields can be configured once for point-to-point applications.

Our solution implements and delivers the low latency with highest throughput and minimum or no inter-packet gap.

Features

- Implements RFC 768 for UDP.

- Implements RFC 791 for IPv4.

- Implements RFC 2460 for IPv6.

- Supports 32/64/128/256/512-bit wide data paths.

- Can handle data rate up to 100Gbps.

- Multiple user interface options for the data path; AXI4 streaming or Avalon Streaming.

- Supports for VLAN tagged frames according to IEEE 802.1Q.

- Supports user data packets from 1 to 1472 bytes in standard mode.

- Optional Jumbo frames support up to 9000 bytes.

- High performance core with low latency and lowest inter-packet gaps.

- Remove padding from MAC frames.

- Discard datagrams having MAC errors, e.g. CRC error, PHY error.

- Can distinguish between unicast /multicast /broadcast datagrams and discard multicast packets.

- UDP checksum generation and checking at high speed using an efficient pipelined implementation.

- IPv4 checksum generation and checking and discard datagrams if checksum fails.

- Filtering of received frames based on MAC and IP address.

- Encapsulation/De-Encapsulation of MAC header along with UDP and IP.

- Can send ARP Announce and ARP Response Packets.

- Classify ARP and IP packets at L2.

- Classify UDP and ICMP packets at L3.

- Customizable IP layer for version 4 and 6.

- Can discard IP datagrams with invalid fragment offsets flags.

- Forward fragmented IP datagrams to fragment buffer after UDP and IP checksum checking and IP header sanity checks.

- Drops datagrams with invalid IP header fields.

- Implements statistics of frames, datagrams, segments at L2, L3 and L4 respectively.