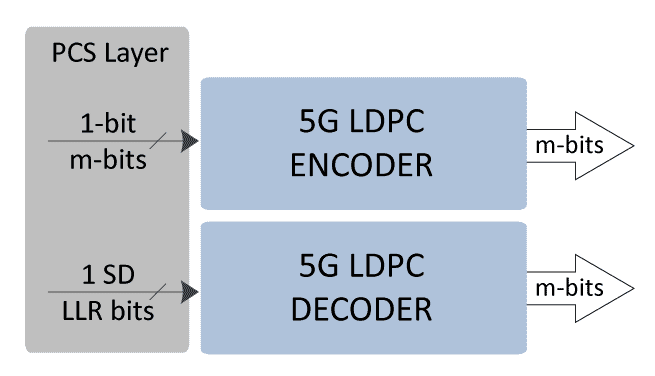

Overview

The 5G NR LDPC Encoder/Decoder IP core implements high throughput, low latency, area-optimized, and highly configurable solutions for both the encoder and decoder, compliant with 3GPP TS 38.212, Release 15 specifications.

Decoder Features

- The decoder core supports 44 different coding rates from 22/23, 22/24, 22/25... down to 22/66 for basegraph 1 and 40 different coding rates from 10/11, 10/12, 10/13... down to 10/50 for basegraph 2.

- The decoder core supports all 51 lifting sizes from the 3GPP 5G standard (from Zc = 2 up to Zc = 384) for both basegraphs.

- The decoder core supports an early termination feature, which can be enabled or disabled on a per-codeword basis.

- For the decoder core, the code rate, base graph, lifting size, and maximum number of iterations (up to 64) are also configurable on a per-codeword basis.

- Decoder Fmax = 560 MHz, occupying 61621 ALMs and 1426 M20K RAM blocks on an Agilex AGFB027R24C2E2VR2 device

Encoder Features

- The encoder core supports 42 different coding rates from 22/25, 22/26, 22/27... down to 22/66 for basegraph 1 (Kb = 22) and 38 different coding rates from 10/13, 10/14, 10/15... down to 10/50 for basegraph 2 (Kb = 10). Additionally, for basegraph 2, the Kb values of 6, 8, and 9 are also supported, resulting in 114 further code rate and message length combinations (38 each for Kb = 6, 8, and 9).

- For basegraph 2 and Kb = 6, 8, or 9, the encoder core automatically appends the required number of filler bits to the message bits.

- The encoder core supports all 51 lifting sizes from the 3GPP 5G standard (from Zc = 2 up to Zc = 384) for both basegraphs.

- The encoder core takes as inputs a fixed 384 bits per clock cycle, where the Zc (equal to lifting size) LSBs contain message bits. The output is also a fixed 384 bits per clock cycle, where the Zc LSBs contain encoded bits.

- Encoder Fmax = 510 MHz, occupying 6784 ALMs and 66 M20K RAM blocks on an Agilex AGFB027R24C2E2VR2 device

For further information, please take a look at the product brief.