Overview

The Reed-Solomon Forward Error Correction (RS-FEC) FPGA IP core solution implements the RS-FEC sublayer specified in IEEE 802.3by/D3.1. This high through-put design is targeted for demanding, high frequency applications and provides bypass capabilities for direct access to sub designs. The target frequency is 390.625MHz for up to 100Gbps operation.

RS-FEC (528,514)

Base RS-FEC

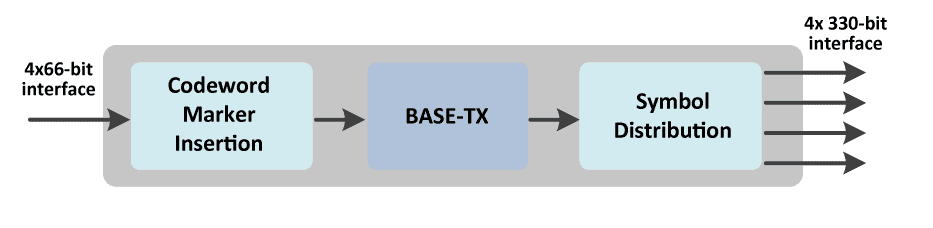

Base-TX

Base-TX Core Features

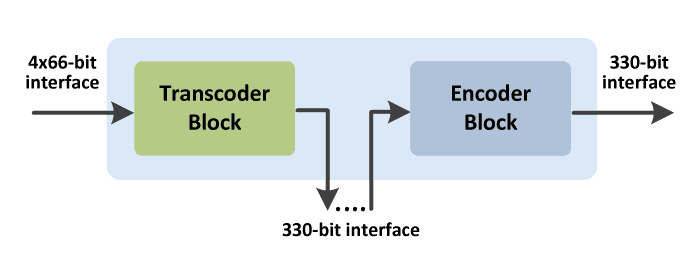

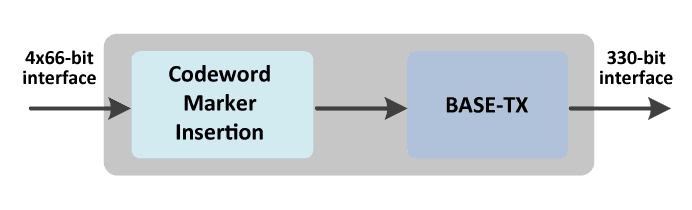

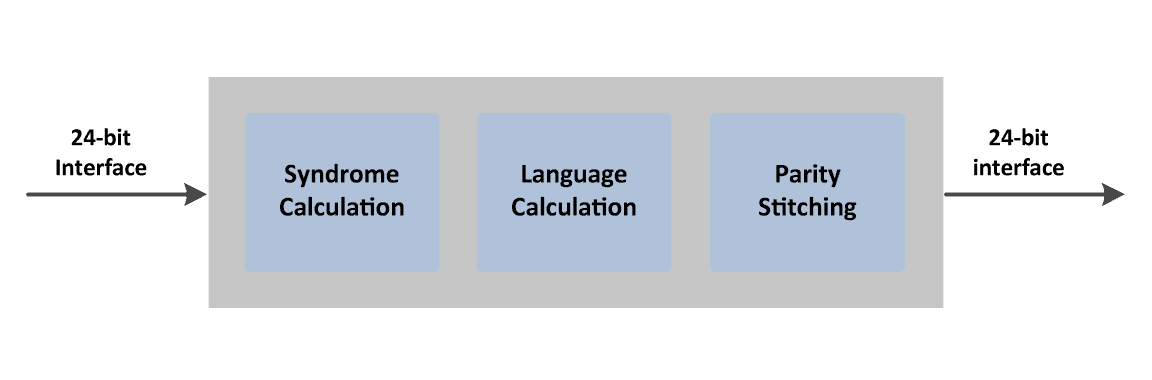

- Implements base modules for the RS-FEC transmitter which includes RS encoder, 64b/66b to 256b/257b transcoder and gearbox logic

- Implements 4x66-bit interface for 64b/66b to 256b/257b transcoder

- Implements 257-bit to 330-bit gearbox logic for interconnection between transcoder and encoder

- Implements 330-bit encoder interface for Reed-Solomon code RS(528,514,10) with polynomial specified in 802.3by specifications

- High through-put, low latency encoder processes 33 symbols in parallel

- Valid based implementation allows discontinuous data flow and/or bandwidth controlled operation

- Implements a fixed latency memory-less design with direct access to RS encoder and transcoder blocks

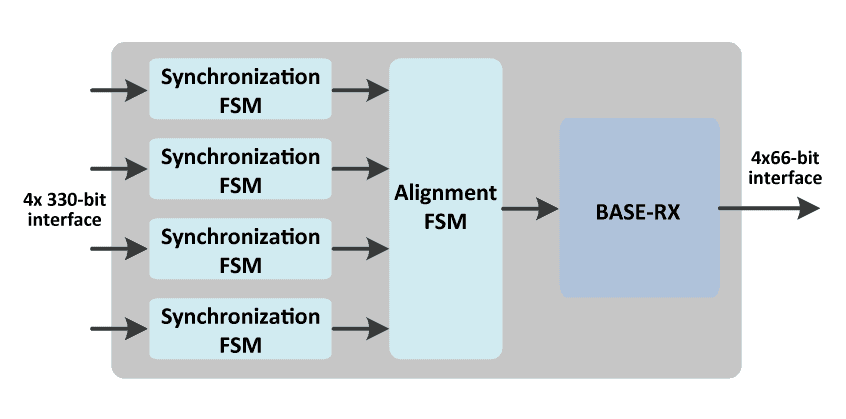

Base-RX

Base-RX Core Features

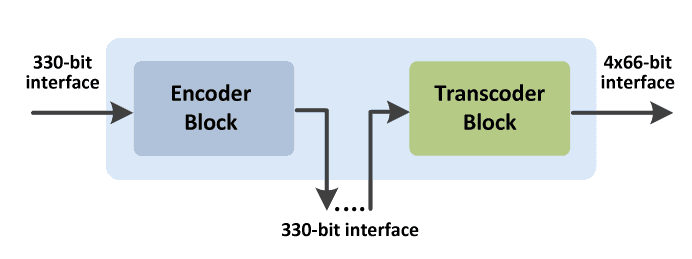

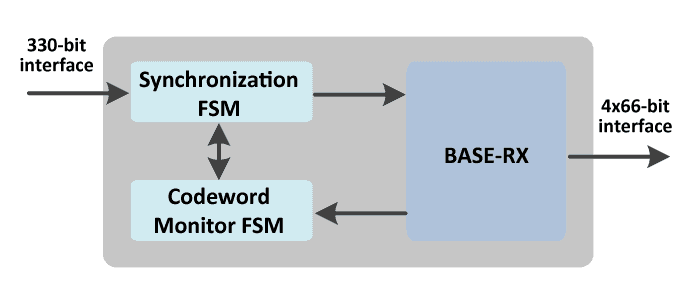

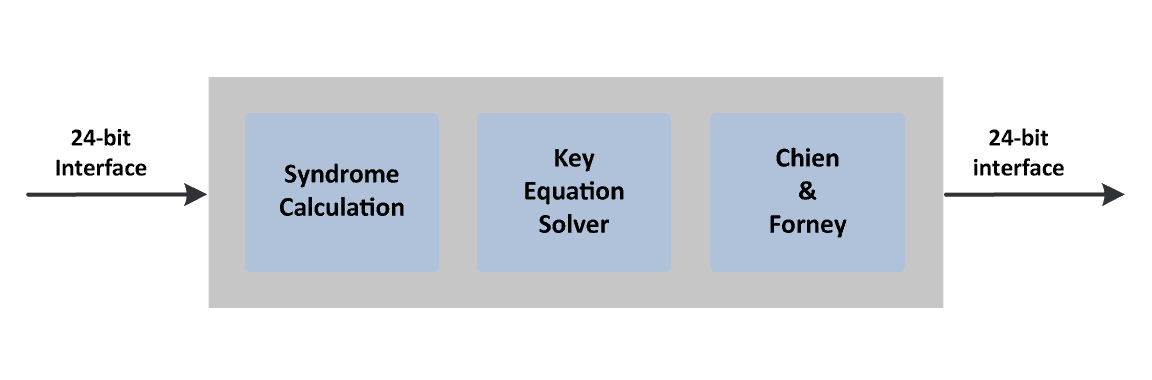

- Implements base modules for the RS-FEC receiver which includes RS decoder a, 256b/257b to 64b/66b transcoder and gearbox logic

- Implements 330-bit decoder interface for Reed-Solomon code (528,514,10) with polynomial specified in 802.3by specifications

- Implements 330-bit to 257-bit gearbox logic for

interconnection between decoder and transcoder - Implements 257-bit interface for 64b/66b to 256b/257b transcoder

- High through-put decoder processes 33 symbols in parallel

- Decoder provides detection of uncorrectable code words and corresponding 257-bit blocks are corrupted at transcoder output as per 802.3by specifications

- Direct access to RS decoder and transcoder blocks is available

25G RS-FEC

100G RS-FEC

RS-FEC (544,514)

RS-FEC (255,239)