Agilex eSOM7 Apollo MxFE Development Platform

Analog Devices (ADI)

Supported Development Kits

- AD9084, AD9088 MxFE

Overview

The eSOM7 wideband development platform for ADI Apollo MxFE (AD9084 and AD9088) provides a quick evaluation and prototyping platform for Altera Agilex™ FPGA based wideband wireless solutions. Designers can leverage high-performance, wideband capabilities of ADI Apollo MxFE® devkits. Development platform consists of two modules:

- An Agilex 7 F-Series FPGA based eSOM7 (embedded System On Module) board with two 400-pin high speed mezzanine connectors

- A carrier board which implements breakout of the FPGA serdes and I/Os.

Apollo carrier can be paired with eSOM-4F or eSOM-2F drop-in compatible SOMs. The eSOM7-4F (4x F-tile) supports all MxFE ADC/ADC channels, whereas the eSOM7-2F (2x F-tile) supports half of all available channels. The carrier module provides a VITA57.4 FMC+ connector with level translation and control logic to interface with ADI sideband Apollo Mixed-Signal Front End (MxFE) evaluation boards.

Features

- Compact 200 x 215mm (7.87” x 8.46”) carrier for Agilex eSOM7 FPGA module designed specifically to interface with ADI Apollo MxFE devkits

- Supports interchangeable eSOMs with different Agilex devices; primarily designed for Agilex 7 I/F series 027/022 density SOMs with 4x F-Tiles

- Designed to provide End-to-End connectivity for broadband wireless development with high bandwidth networking interfaces up to 400Gbps

- Apollo MxFE devkit compatible VITA57.4 FMC+ connector with:

- 24 Serdes lanes up to 32 Gbps for JESD204C connectivity; 2 group of 12 lanes

- JESD clocks and SYSREF signals mapped to FPGA’s true LVDS IOs

- Control, configuration and I/O with level translation mapped through Max10 CPLD on carrier for Apollo devkit

- 1 x QSFP-DD connector for networking interface with 400G/200G/100G Ethernet using F-tile hard IP

- x4 Gen4 (16Gbps) PCIe Gen4 interface through MCIO connector (shared with network F-Tile)

- Up to x16 Gen4 (16Gbps) PCIe Gen4 interface through to MCIO connectors (dedicated mapping to F-Tile)

- 50-pin connector for network synchronizer and interface expansion modules

- Signals mapped to eSOM HPS to support SPI, I2C and UART interfaces

- Differential clock and synchronization signals to support PTP/1588 and SYNCE based network synchronization including JESD 204B/C clock generation

- Integrated USB Blaster II debug interface through micro-USB connector

- Processor and debug interfaces

- HPS Ethernet 1000Base-T via RJ45 connector

- HPS UART and BMC I2C to the USB2.0 connector via USB to UART+I2C bridge

- HPS I2C to the carrier I2C expansion switch and carrier CPLD

- HPS mater SPI to the carrier CPLD with support for FMC+ SPI expansion

- 6-pin ATX and 4-DIN connector for flexible +12V power input

Product Brief

Download to get additional info

Platform Boards

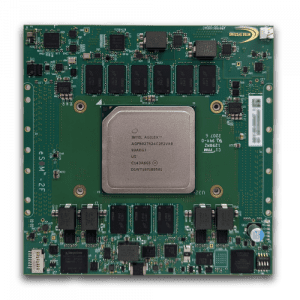

FPGA Board

FPGA Board

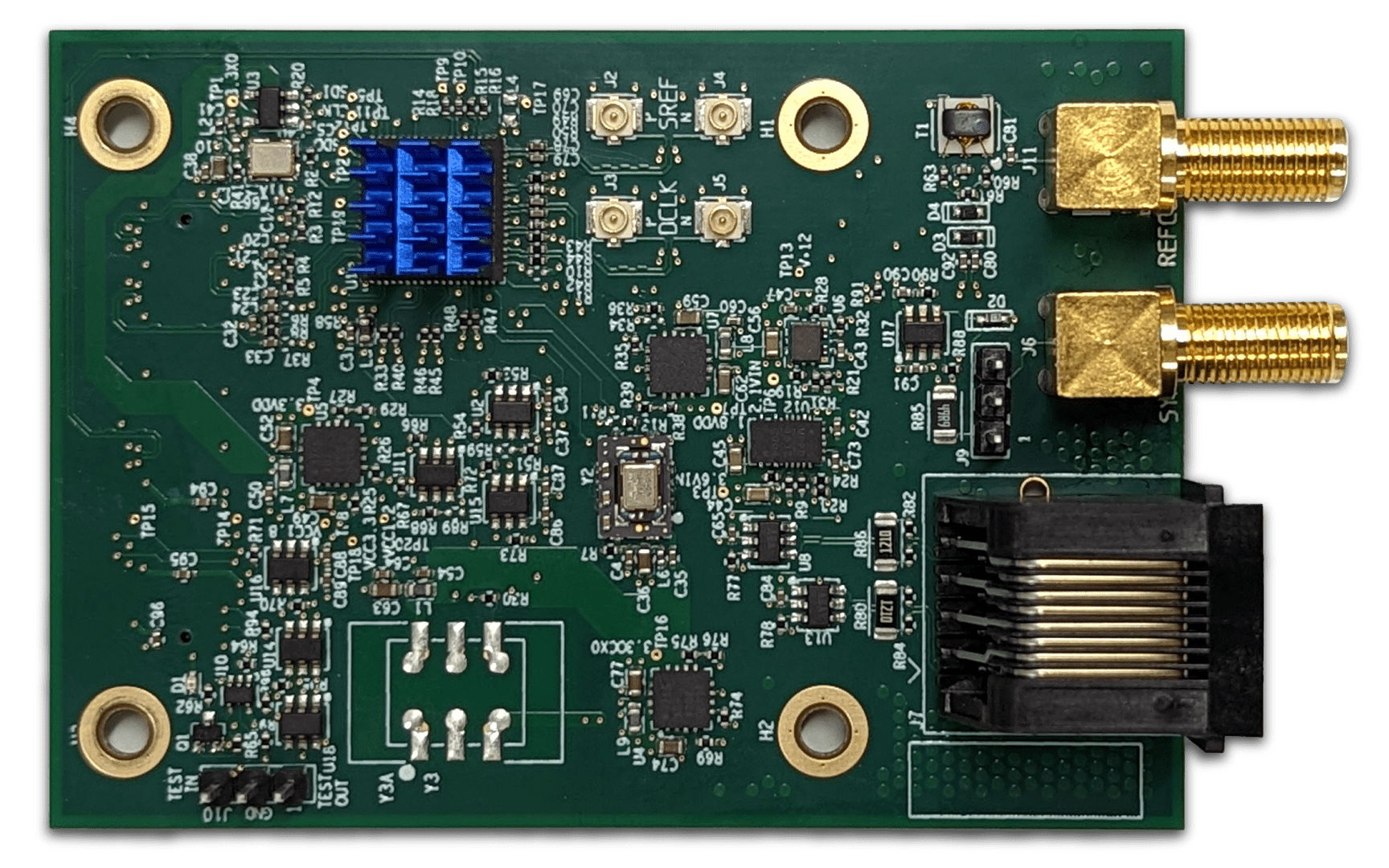

Carrier

Optional Add-Ons

Network Synchronizer Timing Modules

eSOM7 Framework for Apollo MxFE Development (Option)

Features

- Optional FW/SW/Drivers framework for Apollo MxFE. Hardware verified solution designed to minimize development effort and time.

- Integrated JED204C Intel FPGA IP (with F-Tiles) with support for two sets of 12 lanes (24 total) at serdes speed of 27.5Gbps/lane

- N-Channel (up to 8) Playback Controller with support for samples playback from FPGA internal memory or external DDR4 memory

- N-Channel (up to 8) Capture Controller with support for samples capture in FPGA internal memory or deep captures in external DDR4 memory

- Multiplexing logic for user custom post-processing logic at JESD Tx (DAC) path

- Multiplexing logic for user custom pre-processing logic at JESD Rx (ADC) path

- Option for customer IP interface block between network and JESD interface

- Packet filter/routing with support for in-band control Ethernet link through Hitek’s FNIC controller and device driver

- External memory controllers and Avalon-MM Arbitration

- Avalon-MM slave and Address decoder for configuration/status registers on HPS LWH2F interface

- Avalon-MM HPS H2F interface for burst read/write access to external memory (for sample playback/capture files)

- ARM HPS (Hard Processing Subsystem) with Linux support

- Software utilities and tools for sample playback and capture support